微電子學《第五冊》

林昀、唐宏驊

- 出版商: 亞鑫圖書

- 出版日期: 2013-05-24

- 定價: $680

- 售價: 9.5 折 $646

- 語言: 繁體中文

- 頁數: 768

- ISBN: 9868804094

- ISBN-13: 9789868804098

-

相關分類:

微電子學 Microelectronics、電子學 Eletronics

-

其他版本:

微電子學《第五冊》, 2/e

買這商品的人也買了...

-

電力電子學 (Power Electronics, 3/e)

$580$522 -

電力電子學 (Power Electronics: Circuits, Devices, and Applications, 3/e)

電力電子學 (Power Electronics: Circuits, Devices, and Applications, 3/e)$750$712 -

深入淺出物件導向分析與設計 (Head First Object-Oriented Analysis and Design)

深入淺出物件導向分析與設計 (Head First Object-Oriented Analysis and Design)$880$695 -

電磁學天堂祕笈 : 輕鬆解析最實用的馬克士威方程式

電磁學天堂祕笈 : 輕鬆解析最實用的馬克士威方程式$320$252 -

電力電子學綜論, 2/e

電力電子學綜論, 2/e$480$432 -

工程電磁學 (Engineering Electromagnetics, 8/e) (授權經銷版)

工程電磁學 (Engineering Electromagnetics, 8/e) (授權經銷版)$760$722 -

工業電子實習, 4/e

工業電子實習, 4/e$300$270 -

微電子學《第四冊》

微電子學《第四冊》$640$608 -

微電子學《第三冊》

微電子學《第三冊》$700$665 -

101 年電子學試題解析

101 年電子學試題解析$550$522 -

微電子學《第一冊》

微電子學《第一冊》$720$684 -

微電子學《第二冊》

微電子學《第二冊》$680$646 -

電子學分類題庫第一輯

電子學分類題庫第一輯$500$475 -

電子學分類題庫第二輯

電子學分類題庫第二輯$520$494 -

電子學分類題庫第三輯

電子學分類題庫第三輯$610$579 -

電子學分類題庫第四輯

電子學分類題庫第四輯$540$513 -

無瑕的程式碼-敏捷軟體開發技巧守則 + 番外篇-專業程式設計師的生存之道 (雙書合購)

無瑕的程式碼-敏捷軟體開發技巧守則 + 番外篇-專業程式設計師的生存之道 (雙書合購)$940$700 -

泛用伺服馬達應用技術, 3/e

泛用伺服馬達應用技術, 3/e$320$288 -

線性代數聖經 (下), 4/e (適用: 轉學考.資工所.統計所.電機所.數學所)

線性代數聖經 (下), 4/e (適用: 轉學考.資工所.統計所.電機所.數學所)$650$585 -

精通 Python|運用簡單的套件進行現代運算 (Introducing Python: Modern Computing in Simple Packages)

精通 Python|運用簡單的套件進行現代運算 (Introducing Python: Modern Computing in Simple Packages)$780$616 -

無刷直流 BLDC 馬達控制實務- 使用 Atmel SAM C21 ARM Cortex-M0+ 控制核心

無刷直流 BLDC 馬達控制實務- 使用 Atmel SAM C21 ARM Cortex-M0+ 控制核心$780$663 -

Processing入門|互動式圖形實作介紹, 2/e (Make: Getting Started with Processing: A Hands-On Introduction to Making Interactive Graphics, 2/e)

Processing入門|互動式圖形實作介紹, 2/e (Make: Getting Started with Processing: A Hands-On Introduction to Making Interactive Graphics, 2/e)$480$379 -

解析 Linux 驅動程式設計

解析 Linux 驅動程式設計$320$250 -

Python 程式設計「超入門」

Python 程式設計「超入門」$420$357 -

Python 大數據特訓班:資料自動化收集、整理、分析、儲存與應用實戰 (附近300分鐘影音教學/範例程式)

Python 大數據特訓班:資料自動化收集、整理、分析、儲存與應用實戰 (附近300分鐘影音教學/範例程式)$450$355

商品描述

第十八章 振盪電路與波形產生器

簡介

第一部分 弦波振盪電路

18-1 弦波振盪器的觀念

18-1.1 基本觀念

18-1.2 弦波振盪器的實際考量

18-2 OPA同相放大器式的弦波振盪

18-2.1 設計思惟與所需的放大器

18-2.2 Sallen-Key弦波振盪器

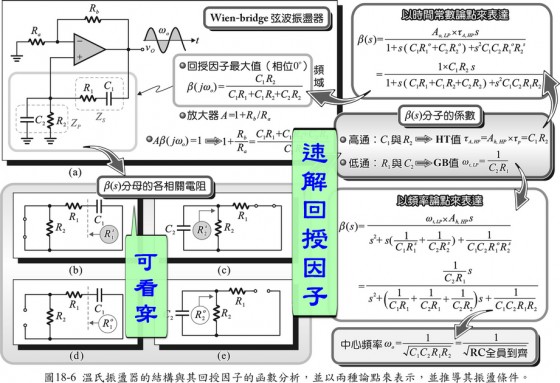

18-2.3 溫氏電橋(Wien-bridge)振盪器

18-2.4 RLC帶通回授型振盪器

18-3 針對OPA反相電路的弦波振盪設計

18-3.1 相位響應為單純的OPA放大器

18-3.2 搭配於OPA反相電路的RC回授網路

18-4 配合於OPA反相放大器的RC相移振盪器

18-4.1 回授網路為三階基本高通RC式

18-4.2 回授網路為三階全極點RC式

18-5 配合於反相微分器的RC相移振盪器

18-6 配合於反相積分器的RC相移振盪器

18-6.1 回授網路為二階全極點RC式

18-6.2 正交振盪器

18-7 單極點反相放大器串接的弦波振盪器

18-7.1 三相振盪器

18-7.2 三級環形振盪器

18-8 LC調諧放大器型振盪器

18-8.1 基本觀念與電路架構

18-8.2 針對共源放大器的LC調諧振盪器

18-8.3 電壓追隨器型的LC調諧振盪器

18-8.4 共射放大器型的LC調諧振盪器

18-8.5 共基放大器型的LC調諧振盪器

18-8.6 石英晶體弦波振盪器

18-8.7 主動濾波調諧型振盪器

18-9 弦波振盪電路之整理

18-9.1 OPA放大器類的振盪器之整理

18-9.2 LC儲能槽型的振盪器之整理

第二部分 多諧振盪電路

18-10 分類與比較器基本電路

18-10.1 多諧振盪器的分類與概念

18-10.2 比較器的基本電路

18-11 史密特觸發電路

18-11.1 基本OPA史密特觸發器

18-11.2 外加參考電壓的史密特觸發器

18-12 OPA的無穩態複振電路

18-12.1 方波自發振盪的電路概念

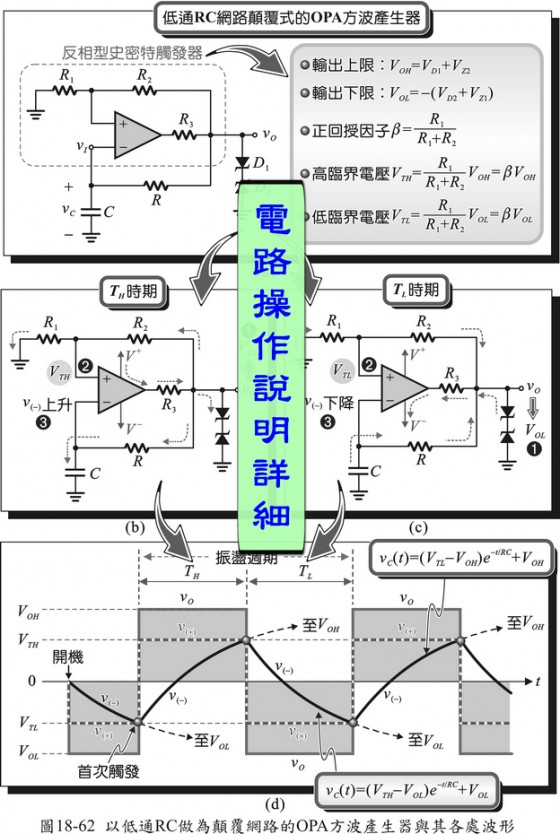

18-12.2 低通RC顛覆式的OPA複振器

18-12.3 同相積分顛覆式的OPA複振器

18-12.4 反相積分顛覆式的OPA複振器

18-12.5 電壓至頻率線性轉換的多諧振盪器

18-13 OPA的單穩態複振器

18-13.1 由無穩態改裝成的單穩態電路

18-13.2 以高通RC正回授的單穩態複振器

18-13.3 可再觸發式的單穩態電路

18-14 555計時IC的振盪電路

18-14.1 555 IC之介紹

18-14.2 555 IC的無穩態複振器

18-14.3 555 IC的單穩態複振器

附錄 溫氏電橋的介紹

第十九章 MOS數位組合電路

簡介

19-1 基本觀念

19-1.1 類比信號與數位信號

19-1.2 邏輯代數基礎與基本邏輯閘符號

19-1.3 邏輯函數的描述方式與化簡

19-1.4 數位電路的分類方式

19-1.5 數位IC以製程技術分類的各族群

19-2 邏輯反相器的概念

19-2.1 理想的反相器

19-2.2 實際反相器的特性考量

19-3 全NMOS反相器電路

19-3.1 線性電阻負載NMOS反相器

19-3.2 增強型負載NMOS反相器

19-3.3 空乏型負載NMOS反相器

19-3.4 NMOS邏輯電路

19-4 互補式CMOS反相器

19-4.1 靜態操作之特性與分析

19-4.2 雜訊邊限與其探討

19-4.3 供應電源縮小的影響

19-4.4 CMOS反相器的佈局圖

19-4.5 CMOS反相器的切換動態特性

19-4.6 CMOS反相器的優點與缺點

19-5 CMOS邏輯電路

19-5.1 結構合成的設計方式

19-5.2 電晶體尺寸的設計

19-5.3 CMOS的NAND閘

19-5.4 CMOS的NOR閘

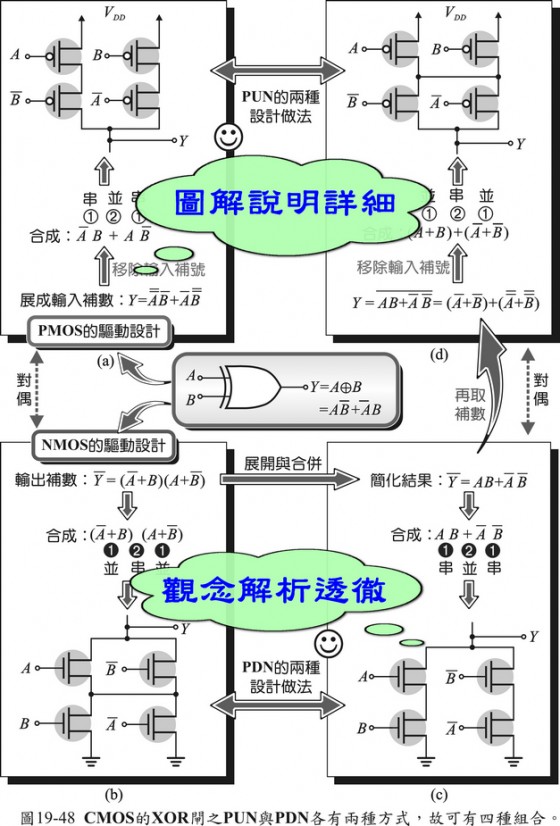

19-5.5 CMOS的XOR閘

19-5.6 CMOS的兩種特殊邏輯閘

19-5.7 CMOS的全加法器電路

19-5.8 CMOS邏輯閘的缺點

19-6 Pseudo-NMOS邏輯電路

19-6.1 Pseudo-NMOS反相器

19-6.2 Pseudo-NMOS邏輯閘

19-7 傳通電晶體與傳輸閘邏輯電路

19-7.1 單一電晶體的PTL

19-7.2 改良的PTL與CPL

19-7.3 CMOS傳輸閘邏輯電路

19-8 動態邏輯電路

19-8.1 基本概念與結構

19-8.2 動態邏輯電路的非理想效應

19-8.3 骨牌CMOS邏輯

第二十章 記憶體電路

簡介

20-1 正反器電路

20-1.1 閂鎖器與正反器的概念

20-1.2 CMOS的正反器電路

20-2 半導體記憶體的形式與架構

20-2.1 記憶體的分類

20-2.2 記憶體晶片的組織

20-3 隨機存取記憶單元RAM

20-3.1 靜態記憶體單元(SRAM)

20-3.2 動態記憶體單元(DRAM)

20-4 感測放大器與位址解碼器

20-4.1 針對SRAM的感測放大器

20-4.2 動態閂鎖器型的感測放大器

20-4.3 針對DRAM的感測放大安排

20-4.4 列位址解碼器

20-4.5 行位址解碼器

20-5 唯讀記憶體(ROM)

20-5.1 固定的MOS RAM

20-5.2 光罩可程式化ROM

20-5.3 場式可程式化的PROM

20-5.4 可抹除可程式化EPROM

20-5.5 電式可抹除可程式化E2PROM

20-5.6 快閃記憶體

20-6 數位多諧振盪電路

20-6.1 數位單穩態電路

20-6.2 CMOS閘無穩態複振器

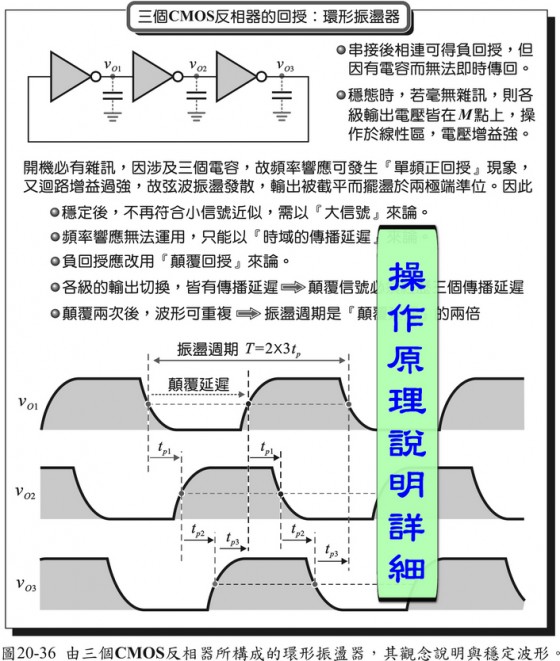

20-6.3 CMOS反相器的環型振盪器

第二十一章 BJT數位電路

簡介

21-1 電阻-電晶體-邏輯RTL

21-1.1 BJT基本反相器

21-1.2 RTL電路

21-2 二極體-電晶體-邏輯DTL

21-2.1 DTL的理念與演變

21-2.2 靜態特性分析與扇出問題

21-2.3 改良式DTL

21-3 電晶體-電晶體-邏輯TTL

21-3.1 基本型TTL

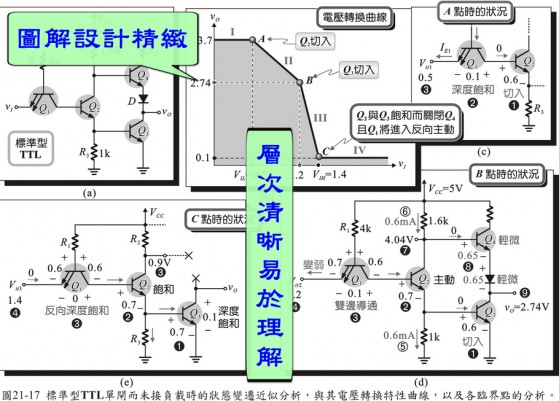

21-3.2 圖騰柱結構TTL(標準型TTL)

21-3.3 標準型TTL外接之改良

21-3.4 改良圖騰柱式TTL

21-4 性能提升的TTL

21-4.1 蕭基TTL(STTL)

21-4.2 低功率蕭基TTL(LSTTL)

21-4.3 高等低功率蕭基TTL(ALSTTL)

21-5 射極耦合邏輯ECL

21-5.1 電路結構與安排理念

21-5.2 電路設計與特性分析

21-5.3 ECL的信號傳輸特性與優缺點

21-6 BiCMOS數位電路

21-6.1 BiCMOS反相器

21-6.2 BiCMOS邏輯閘